Наверняка, кто хотя бы раз держал в руках классическую «плашку» оперативной памяти RAM, занимался «оверклокингом» памяти или работает, например, программистом — задумывался о том, как же физически устроена оперативная память «под капотом»? Все эти страшные слова про тайминги, ранги, банки, стандарты DDR и т.д. обычно ничего не говорят рядовому пользователю.

А возможно вы даже что-то там и слышали про ячейки и банки памяти, ранги, каналы памяти и т.д. — но в совокупности есть каша в голове и не хватает какой-то общей картины всего происходящего? Не переживайте — вы не один такой. Автор этих строк когда-то давно тоже был далек от всей этой технической «магии», пока по крупицам не изучил вопрос, дабы постараться изложить его в удобочитаемом и понятном виде — что называется «для самых меленьких».

Данная же статья будем первой по счету из небольшого цикла статей по данной теме. Сегодня разберем общую вводную структуру по оперативной RAM памяти, а остальные нюансы выделим в отдельные материалы, которые будут опубликованы позже.

Немного про типы памяти

У каждого компьютера, как и у фактически любого вычислительного устройства, есть ОЗУ (оперативное запоминающее устройство, она же оперативная память, она же RAM, т.е. random-access memory — память с произвольным доступом), встроенное в процессор или находящееся на отдельной плате, в виде микросхемы; вычислительные устройства просто не смогли бы работать без оперативной памяти.

Существует по меньшей мере два основных типа RAM: статическая и динамическая, или сокращённо SRAM и DRAM (от приставок static и dynamic соответственно). Конечно это не единственные существующие в природе типы RAM, есть еще допустим память на RS-триггерах, но сейчас лесть в эти дебри мы не будем, как и углубляться в подробные отличия между двумя вышеуказанными типами памяти.

Отметим лишь, что общей особенностью и SRAM и DRAM является постоянная энергозависимость для хранения информации. Если питание пропадает, то и данные также потеряются (в отличие от той же ПЗУ, т.е. памяти типа ROM, сокращение от read-only memory - тема пожалуй для отдельной статьи).

Исторически так сложилось, что все современные модули памяти построены именно на DRAM. За примером долго ходить не надо: модули памяти представленные платами типа DIMM (по сути всем нам хорошо известная классическая «оперативка» стандарта DDR(x), которую вы наверняка хотя бы раз в жизни меняли в своем ПК или ноутбуке) выполнены именно на базе DRAM.

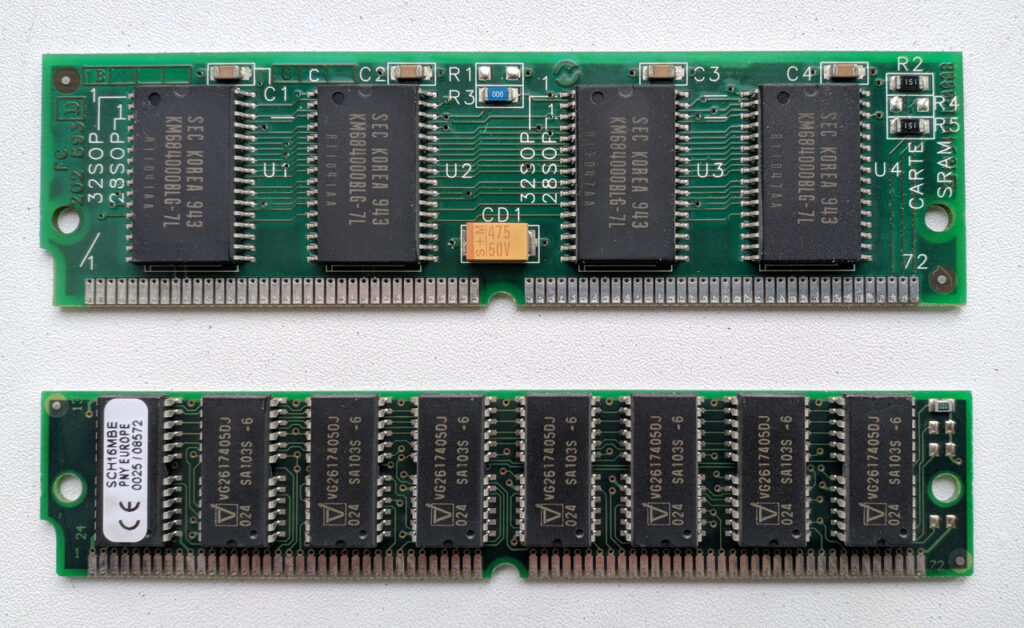

На картинке выше вы можете видеть пример старой памяти в форм-факторе SIMM: 2 Mb на базе SRAM (сверху) и 16 Mb на базе DRAM (снизу). Модули памяти SRAM в своем «внешнем» исполнении, как класс в принципе, изжили себя еще в конце 90‑х годов прошлого столетия. А DRAM память успешно существует и по сей день, правда не в форм-факторе SIMM, а перекочевала в ее наследного собрата: платы типа DIMM (например, DIMM DDR5).

DRAM имеет гораздо более высокую плотность записи и невысокую производственную стоимость по сравнению с памятью SRAM. Тем не менее, из этого не стоит делать вывод, что SRAM это уже какой-то устаревший и никому не нужный тип памяти. В свою очередь, в сравнении с DRAM, память SRAM имеет преимущества в виде невероятно быстрого произвольного доступа к ячейкам памяти, а также относительно низкое энергопотребление.

Свое массовое применение SRAM нашла для регистров и кэш-памяти современных процессоров. Хотя также иногда может встречаться и в микроконтроллерах некоторых плат, распаянных напрямую, во внешнем исполнении TSOP (одна из разновидностей корпусов современных микросхем).

Далее в рамках данной статьи мы будем рассматривать память только DRAM, т.е. ответим на вопросы: где обычно находится DRAM, как она устроена и как работает?

Где обитает этот зверь — DRAM?

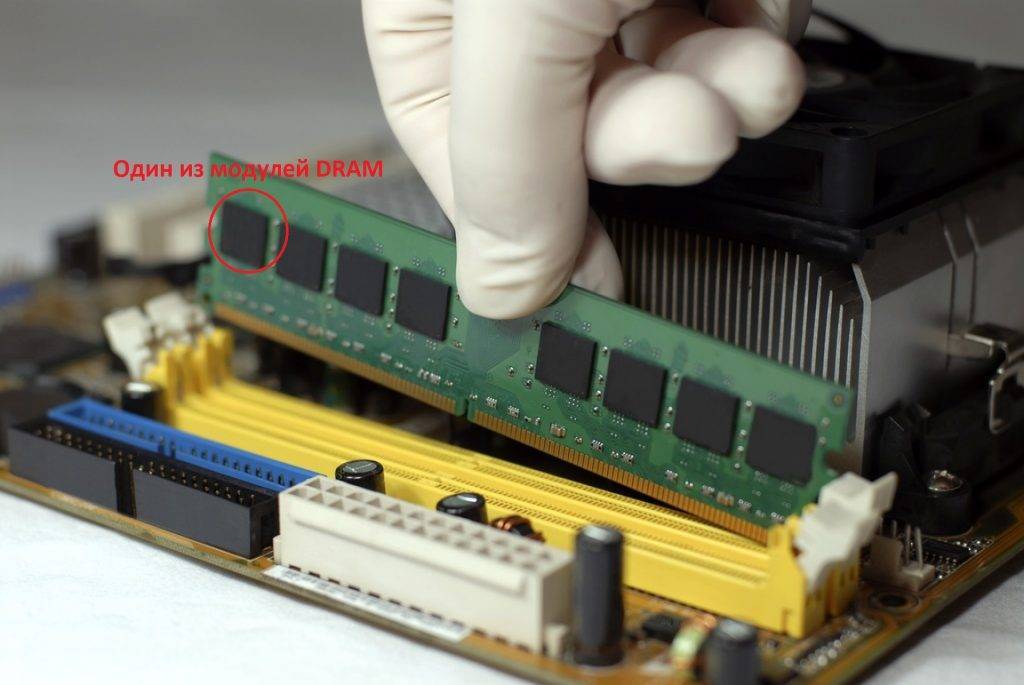

Большинству людей, которые хоть раз заглядывали в недра системного блока ПК, память DRAM знакома в виде набора несколько её «планок» находящихся рядом с CPU (центральным процессором или сокращенно ЦП). Эту группу DRAM часто называют системной памятью, но правильнее её конечно называть памятью процессора. И хотя в данном случае эта память не встроена напрямую в CPU, а располагается рядом — она является основным накопителем рабочих данных и команд самого процессора!

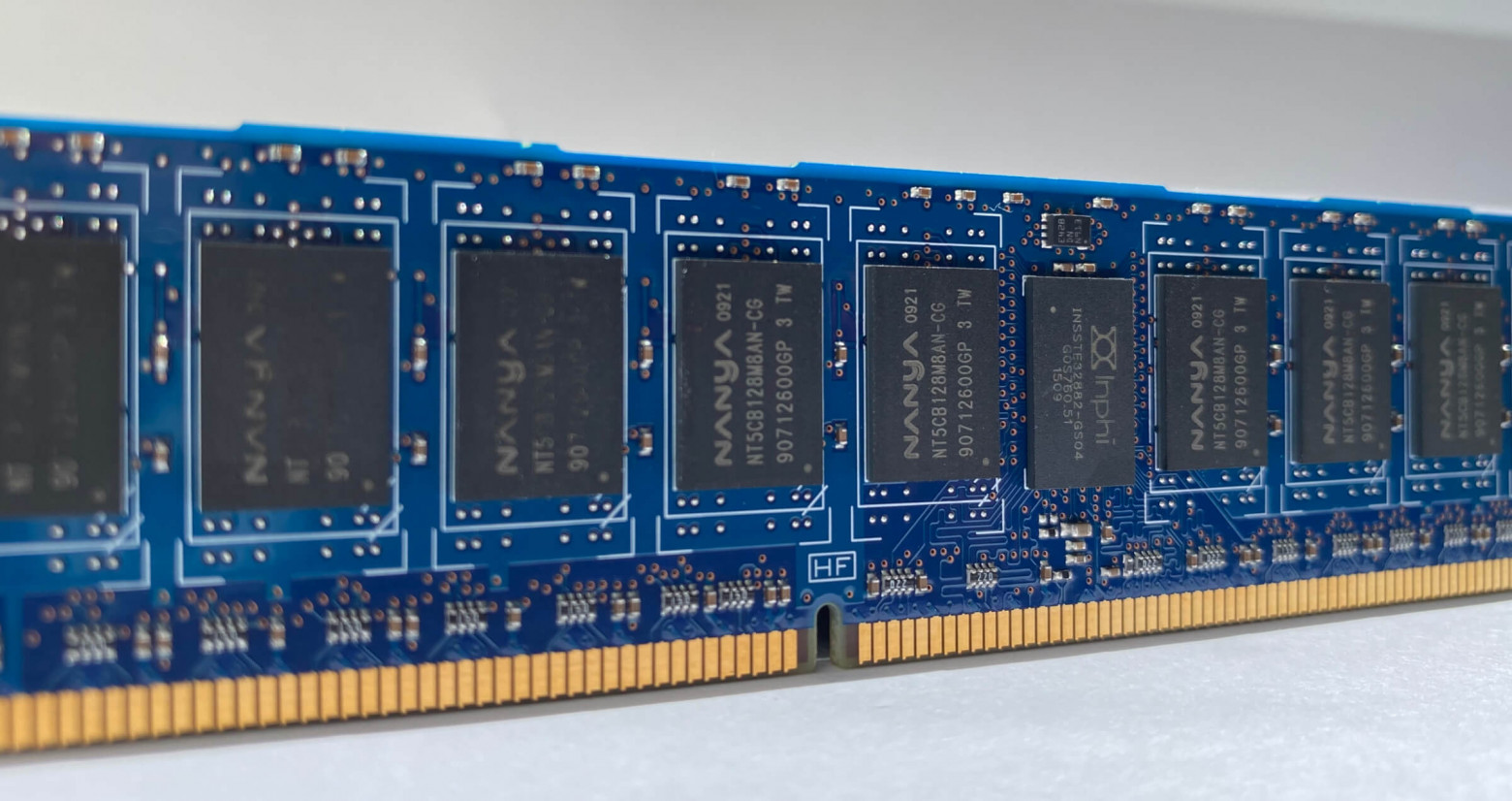

Как видно на представленном выше изображении, чипы DRAM (иногда также называемые модулем) находятся на небольшой плате, вставляемой в материнскую (системную) плату через специальный слот. Каждая плата, на которой расположена группа чипов DRAM, обычно сегодня представлена форм-фактором DIMM (англ. Dual Inline Memory Module — двухсторонний модуль памяти).

В простонародье их также именуют «планками ОЗУ», «плашками памяти», «ди-ди-эр-ками» и пр. Это самое известное конструктивное решение DRAM любого современного компьютера, хотя бывают в природе (пусть уже и не встречающиеся в общем-то в современных ПК) и другие разновидности плат: SIPP, SIMM, RIMM и д.р.

В компактных устройствах, например некоторых современных моделях неттопов или ноутбуков, память не обязательно может подключаться через внешнюю плату, а сразу быть распаяна напрямую на материнской плате.

Ещё одним местом, где можно найти набор чипов памяти — является графическая (видео) карта. Ей требуется сверхбыстрая DRAM, потому что при 3D-рендеринге выполняется огромное количество операций чтения и записи данных. Этот тип DRAM предназначен для несколько иного использования по сравнению с типом, применяемым в системной памяти CPU.

Ниже вы можете видеть пример платы с GPU (англ. Graphics Processing Unit), окружённый двенадцатью небольшими пластинами — это так же чипы DRAM. В данном случае это тип памяти стандарта GDDR5X.

Обычно графическим картам не нужно столько же памяти, сколько CPU, но их объём всё равно может достигать нескольких Гигабайт. А тепловыделение, из за более высоких скоростей, так же гораздо выше.

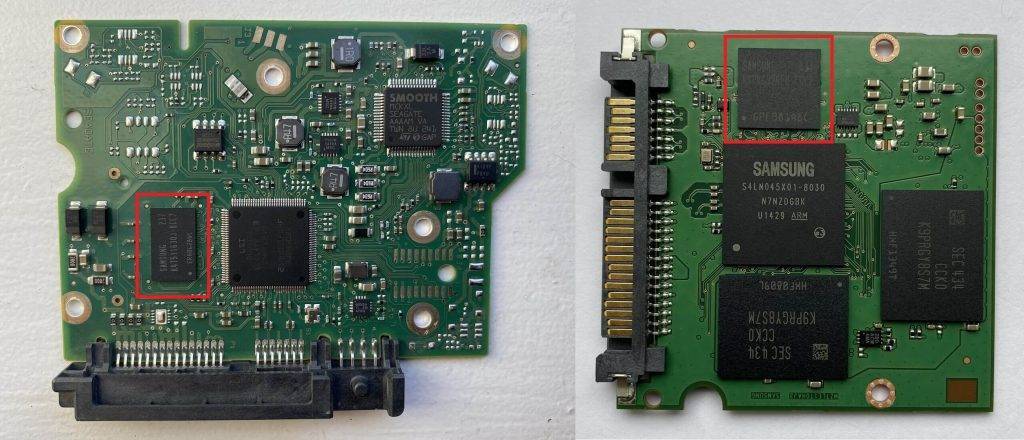

Не каждому устройству в компьютере нужно столь много памяти: например, жёстким дискам (HDD) достаточно небольшого количества DRAM, в среднем до 256 МБ. Она используются там для группировки данных перед записью на диск. Для SSD дисков может использоваться чуть больше, например 512 или 1024 МБ.

На фотографиях выше мы видим платы HDD (слева) и SSD (справа), на которых отмечены чипы DRAM. Заметили, что чип всего один? Даже 1024 МБ сегодня не такой уж большой объём для DRAM чипа, поэтому вполне достаточно одного модуля памяти.

Узнав, что каждый компонент или периферийное устройство, выполняющее обработку, требует RAM, вы сможете найти память во внутренностях не только любого ПК, но и фактически во всех цифровых устройствах. На контроллерах SATA и PCI Express установлены небольшие чипы DRAM. У сетевых интерфейсов и звуковых карт они тоже есть, как собственно и у принтеров, и даже у современных SMART-телевизоров и «умных» колонок.

Как устроена DRAM «под капотом»?

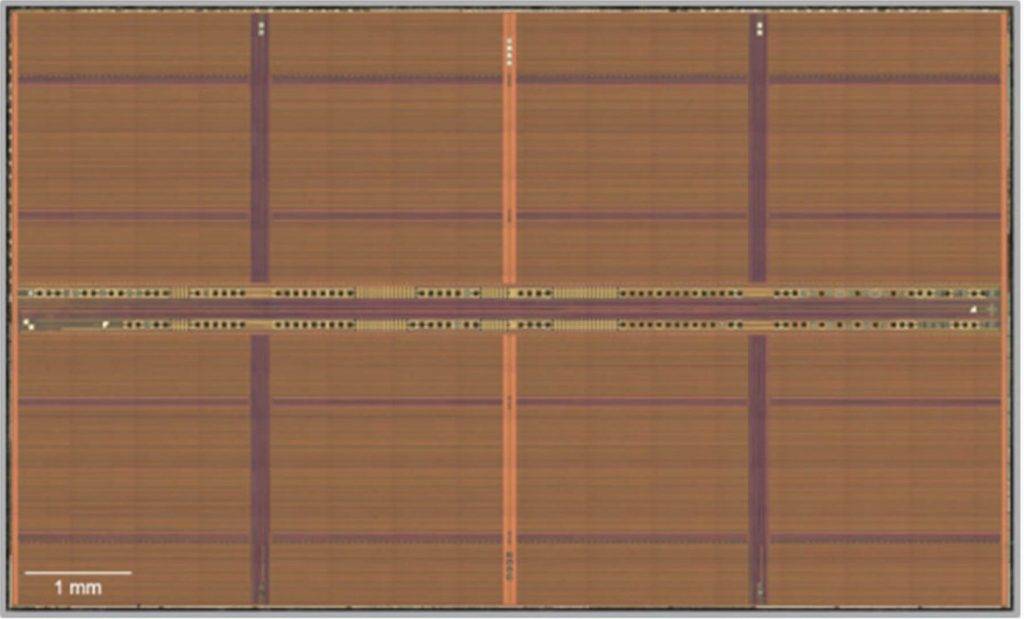

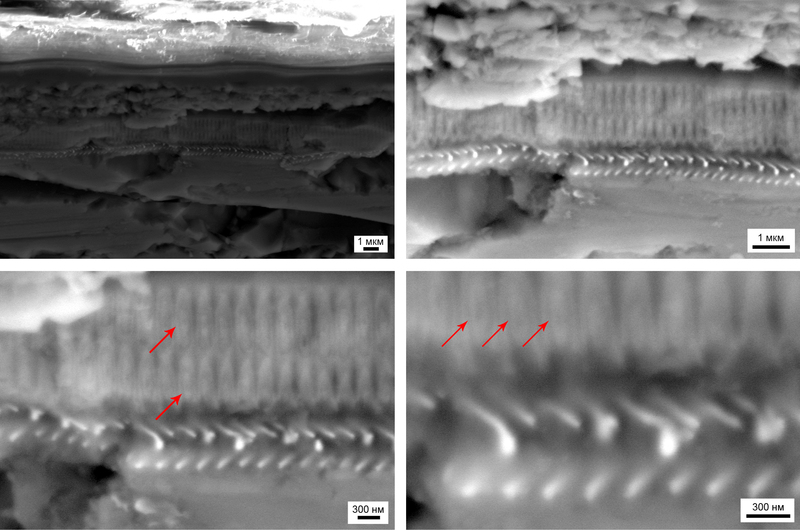

Если взять один из таких чипов DRAM, аккуратно снять с него крышку и посмотреть под увеличением, то можно увидеть что-то вроде такой картины:

И разумеется нет — это не спутниковая фотография поля засеянного пшеницей, с тропинками для проезда техники. Скорее — это поле засеянное ячейками памяти, различными линиями связи и прочими компонентами.

Здесь мы столкнулись с таким понятием как ячейка памяти. Рассмотрим ее чуть подробнее «под микроскопом».

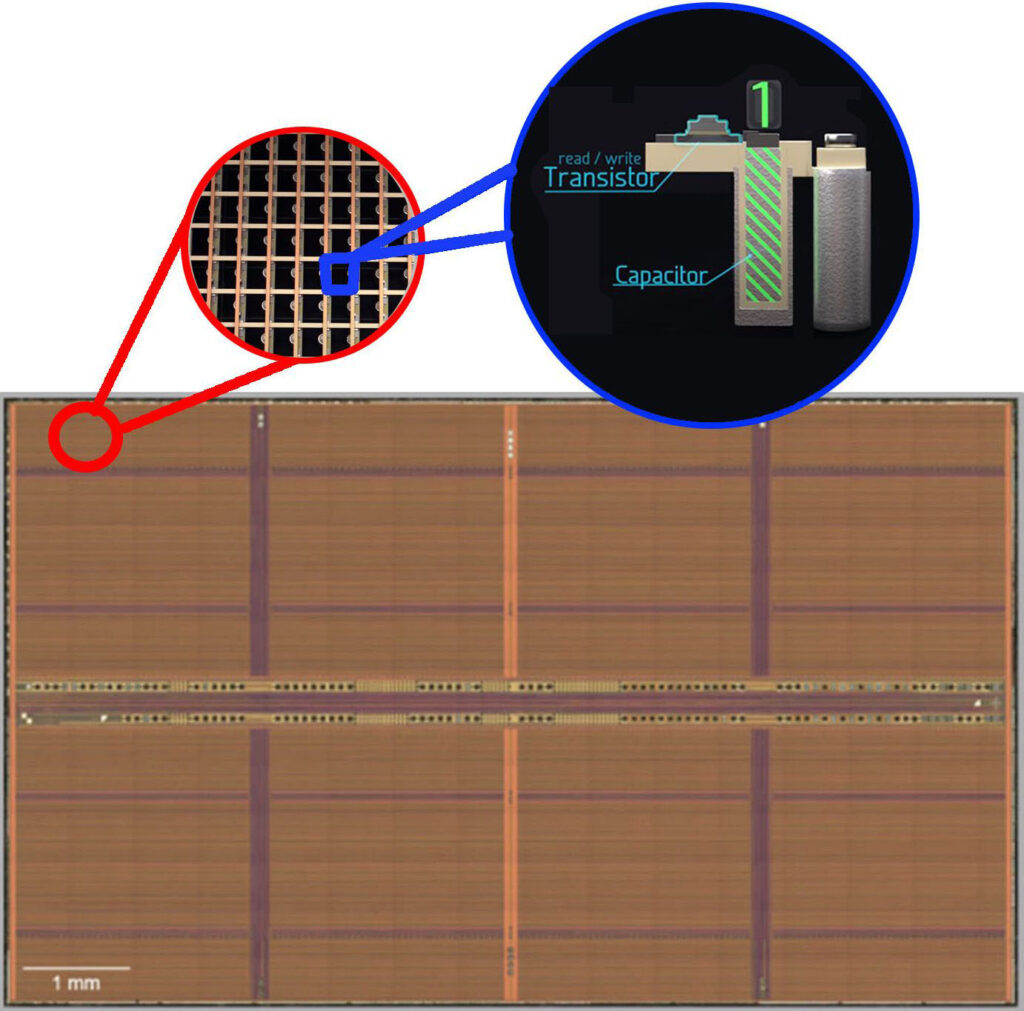

По сути, ячейка в DRAM состоит из 2 компонентов:

- Переключателя (вентиля), представленного в виде MOSFET (МОП-транзистора)

- Накопителя, представляющего собой конденсатор.

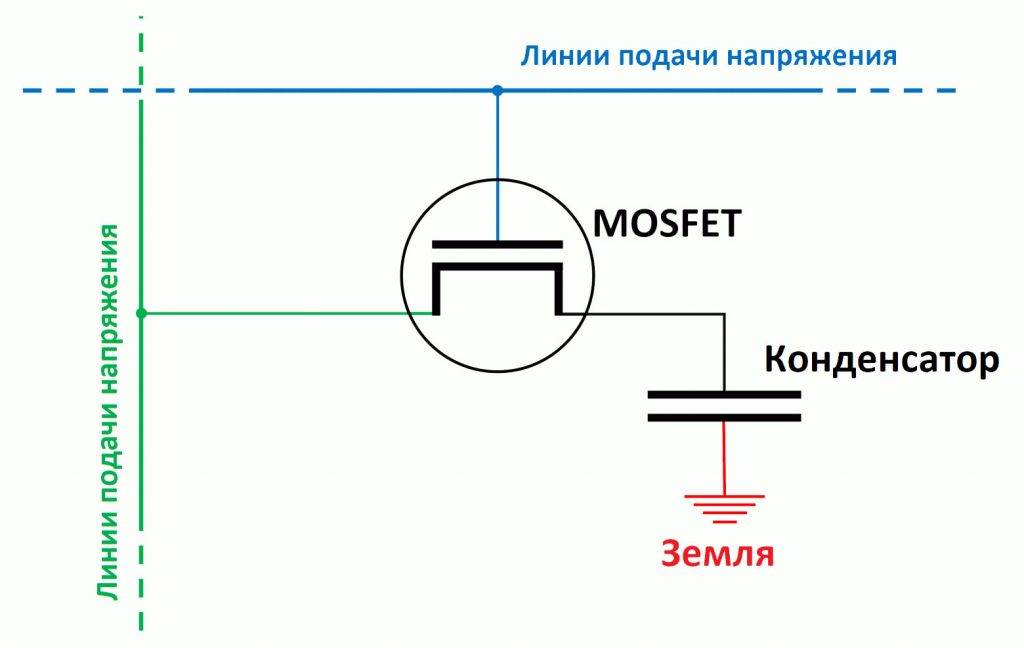

Очень условно эту область можно представить в виде схемы:

Синими и зелёными линиями обозначены соединения, подающие напряжение на МОП-транзистор и конденсатор. К каждой такой линии подключена целая группа ячеек. Эти линии используются для считывания и записи данных в ячейку, причем первой всегда срабатывает вертикальная (зеленая) линия, которую обычно называют — битовая линия (англ. Bitline).

При подаче напряжения на битовую линию включается (открывается) транзистор и электроны могут течь через канал, тем самым подключая конденсатор к битовой линии. Это позволяет получить доступ к конденсатору и зарядить его до определенного значения (т.е. поднимая до определенного уровня напряжения Vdd), либо наоборот почти полностью разрядить.

Конденсатор тут используется в качестве некого «сосуда» для заполнения электрическим зарядом — его пустое или заполненное состояние выражается в условных единицах данных, называемых битами: при значении 0 — конденсатор опустошен, при 1 — конденсатор заполнен.

Таким образом у нас появляется возможность считывать данные с ячейки, измеряя количество заряда, при помощи так называемых усилителей считывания, подключенных к горизонтальной (синей) линии слова (англ. worldline). Когда линия слова отключается и соответственно выключен сам транзистор, конденсатор изолируется от битовой линии, сохраняя при этом данные (заряд), которые были записаны в него ранее.

Разумеется габариты конденсатора ячейки DRAM далеко не те, что можно наблюдать невооруженным глазом в качестве, например, SMD компонентов на материнской плате. Конденсаторов в современных ячейках DRAM несколько миллиардов, их размеры не превышают и 300nm (нанометров) в длину, а шаг между конденсаторами вообще может быть шириной всего в пару десятков атомов. Размеры же самого транзистора и затвора еще меньше.

Вследствие таких малых размеров, не смотря на предпринятые инженерами усилия, конденсаторы не способны хранить в себе накопленный заряд сколько-то долго и в считаные миллисекунды он утекает (просачивается через канал транзистора). Это означает, что каждую ячейку DRAM нужно постоянно обновлять (англ. refresh) в среднем от 15 до 60 раз в секунду.

К сожалению во время процесса обновления ячеек в них невозможно считывание и запись данных, т.е. необходимо сначала это процесс в какой-то степени поставить на паузу, затем считать\записать данные с ячейки, затем продолжить. Именно по этому память типа SRAM гораздо быстрее, т.к. ячейки памяти там основаны не на конденсаторах, а на других элементах, что избавляет от процедуры постоянной перезарядки.

Вообще, чем дольше ячейка памяти способна удерживать заряд без подпитки (т.е. чем реже ее обновление), тем выше скорость чтения\записи данных. С другой стороны и тем выше вероятность потери данных вследствие утечки заряда (вероятность эта зависит также и от температуры ячеек памяти, росту которой плодотворно способствует пресловутый «разгон» оперативки). Поэтому должна быть некая золотая середина между этими двумя крайностями, которая по сути регламентируется производителем конкретного чипа DRAM.

Строго говоря, заряд со временем «утекает» из ячейки любого типа памяти, не только RAM, но и ROM. Интересная закономерность, что тем быстрее память, тем выше скорость такого утекания. RAM не способна хранить заряд и 1 секунду. Память ROM, например на базе NAND-памяти, может хранить заряд несколько лет. Накопители на магнитной основе, могут его хранить уже несколько десятков лет. А представленные не так давно компанией Microsoft накопители на базе стеклянных пластин, способны хранить информацию несколько тысяч (!) лет, причем им не страшны ни магнитные, ни рентгеновские излучения!

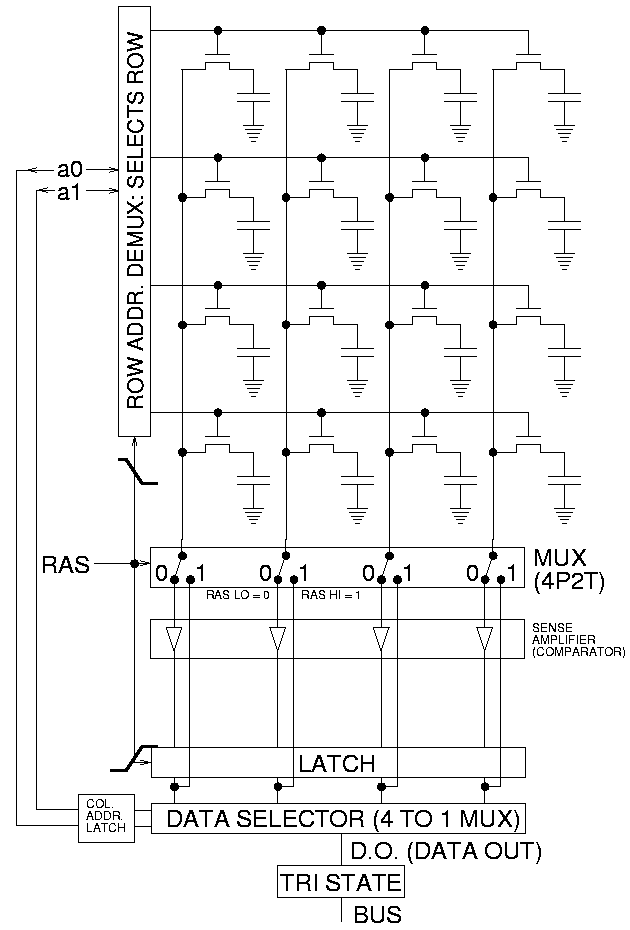

В интернете можно найти вот такую картинку, представляющую собой локальную схему соединения ячеек памяти внутри DRAM (хотя это все еще является довольно упрощенным представлением).

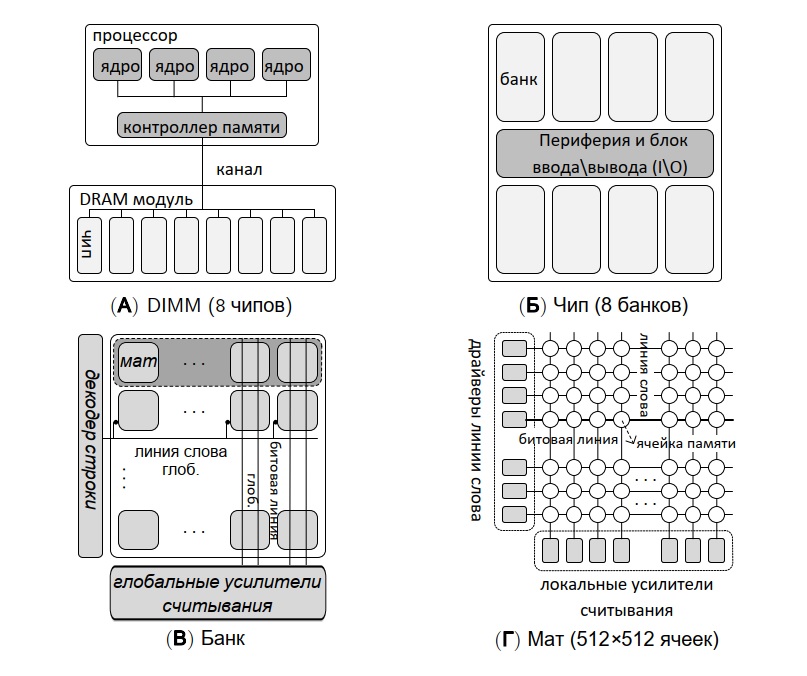

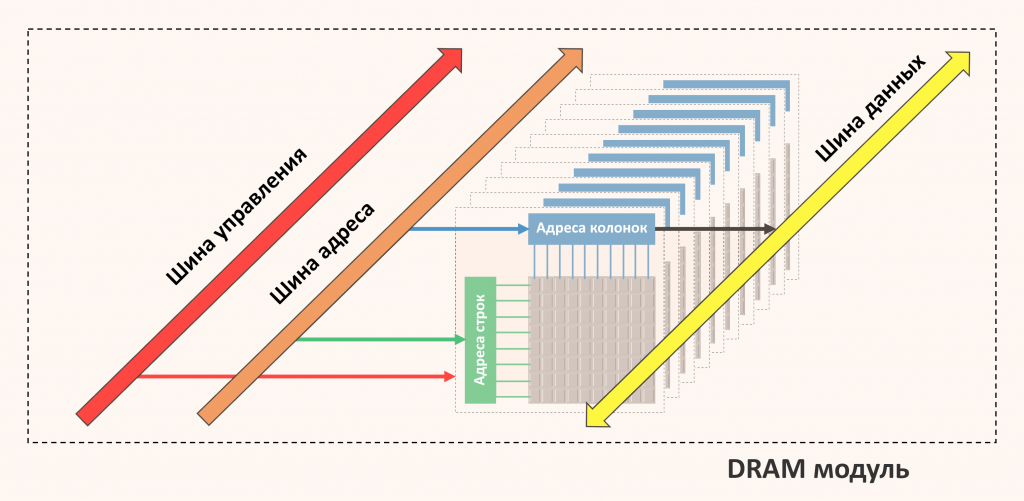

Если опустить подробности, то можно сказать, что модуль DRAM представляет собой двумерный массив ячеек памяти, соединенных различными линиями связи и подключенных к периферии (через блок I\O), а также сгруппированных в специальные структуры, так называемые банки памяти, состоящие из буферов адреса строки (или как его еще называют - декодер строки) и усилителей считывания (усилители считывания заряда на конденсаторах ячеек памяти). Ниже представлен многоуровневая структура модулей DRAM: в масштабе от модуля DIMM до локального мата памяти.

Масштаб структуры памяти: (А) Плата DIMM -> (Б) Чип -> (В) Банк памяти -> (Г) Мат памяти

Сейчас этим голову можно сильно не забивать. Пока только надо понять, что DRAM имеет сложную, как физическую, так и логическую структуру. «Живая» же фотография продольного среза чипа памяти, увеличенная в сотни раз при помощи мощного микроскопа, выглядит как-то так (красными стрелочками выделены продольные срезы конденсаторов):

Очень условно чип DRAM можно представить в виде огромной «шоколадной плитки» состоящей из множества ее «долек» (строк и столбцов с ячейками памяти).

Горизонтальный набор ячеек памяти, т.е. полная ее их строка, называется страницей, а длина её зависит от типа и конфигурации DRAM. Чем длиннее страница, тем больше в ней бит, но и тем большая электрическая мощность нужна для её работы; короткие страницы потребляют меньше мощности, но и содержат меньший объём данных. При проектировании DRAM инженеры обычно стремятся к получению максимально длинных страниц.

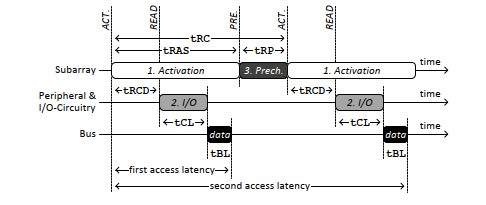

Не будем сейчас заострять внимание, как именно считываются и записываются данные в ячейки, а также как при этом работает блок I\O. Т.к. на это ушел бы еще не один десяток страниц текста и картинок. Просто отметим, что глобально происходит 3 этапа: активация, чтение\запись, предварительная зарядка.

При считывании и записи на чип DRAM первым этапом процесса является так называемая активация всей страницы. Адреса строк (состоящие из нулей и единиц) хранятся в специальном буфере строки (англ. Row Decoder - физически это такая штуковина, которая представляет собой набор усилителей считывания и защёлок). Во время фазы активации буфер строк получает адрес конкретной страницы, и в один момент времени может быть активирована только одна такая строка. Уже затем активируется соответствующий столбец для извлечения данных из этого буфера.

Если страница слишком мала то, чтобы успеть за запросами данных, строки нужно активировать чаще; и наоборот — большая страница предоставляет больше данных, поэтому активировать её можно реже. И даже несмотря на то, что длинная страница требует большей мощности и потенциально может быть менее стабильной, архитектурно она считается более правильной.

На самом деле, помимо вышесказанного, существует зависимость скорости доступа к ячейкам памяти на основе их местоположения в массиве ячеек DRAM. Доступ к некоторым ячейкам памяти возможен быстрее других благодаря их физическому расположению. Это обусловлено структурной организацией DRAM и зависит от ее архитектурной вариации.

Архитектурные вариации, в свою очередь, возникают из-за различия расстояний между ячейками и периферийной логикой, которая используется для доступа к этим ячейкам. Также проводники, соединяющие ячейки с периферийной логикой, сами по себе могут иметь более высокие сопротивления и емкости (которые со временем еще и могут деградировать, например вследствие завышенного напряжения поданного на чип DRAM).

В конечном счете сигнал, бегающий к ячейкам памяти, испытывает задержки, называемые латентностью памяти. Грубо говоря, ячейки ближе к периферийной логике имеют меньшую задержку и могут быть доступны быстрее, чем ячейки, расположенные дальше от периферийной логики — поэтому производителями берется некая усреднённая задержка сигнала, чтобы успеть «сбегать» ко всем ячейкам. Но к теме латентности памяти и задержек мы вернемся позже.

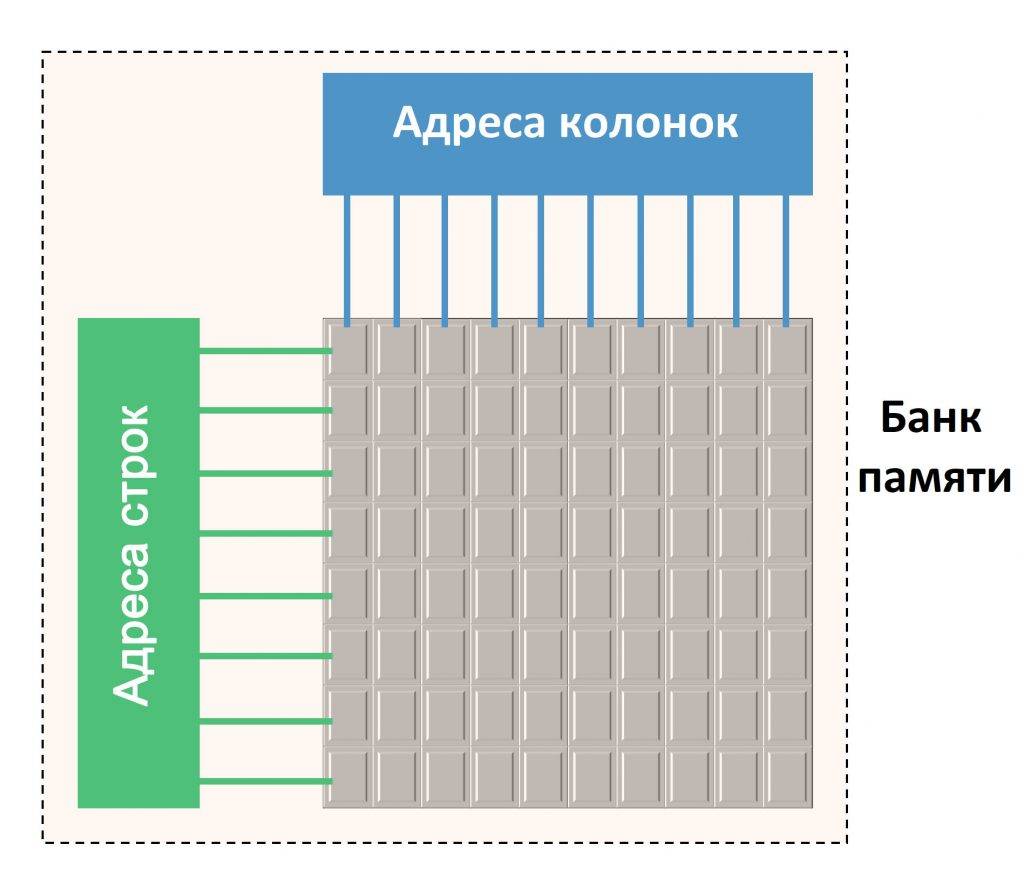

Так вот если собрать вместе набор всех страниц (т.е. совокупность строк и столбцов с ячейками), то мы получим ту самую «плитку шоколада», т.е. один Банк (англ. Bank — хранилище) памяти DRAM. Как и в случае самих ячеек памяти, размер и расположение строк и столбцов с ячейками играют важную роль в количестве хранимых данных, скорости работы памяти, энергопотреблении и так далее.

Допустим, схема одного банка состоит из 4 096 строк и 4 096 столбцов, соответственно полный объём такого банка будет равен 16 777 216 битам (4 096 х 4 096), ну или 2 Мб соответственно. У современных чипов DRAM банки имеют «прямоугольную» структуру, потому что, как мы помним, длинные страницы лучше, чем короткие. Например, структура банка состоящая из 16 384 строк и 1 024 столбцов даст нам все те же 2 Мб (16 384 х 1 024) памяти в сумме, но каждая страница при этом будет содержать в четыре раза больше памяти, чем в «квадратной» схеме.

Разумеется банки памяти в современной DRAM имеют гораздо более высокий объем и плотность, достигающий сотен мегабайт. Например, один чип памяти типа DDR4 объемом 2 Гб состоит из 16 банков по 128 Мб (131 072 х 8 192) каждый.

Все страницы в банках соединены с системой адресации строк и столбцов, которые контролируются сигналами (по шинам) управления и адреса для каждой строки/столбца. Чем больше строк и столбцов в банке, тем больше битов должно использоваться в адресе.

Для увеличения плотности (объёма данных) памяти и увеличения скорости доступа к страницам памяти, современные чипы DRAM могут иметь 16 (DDR4) или даже 32 (DDR5) банка. Это суммарно позволяет увеличить ёмкость одного такого чипа DRAM в среднем до 4 Гб, при использовании памяти в платах DIMM «домашнего» сегмента.

Это интересно! В конце 2021 года компания Samsung представила серверную плату RDIMM стандарта DDR5 емкостью в 512 (!) Гб. На одной такой 512 Гб плашке разместили тридцать два 16-гигабитных восьмислойных чипов памяти (8‑Hi). Объём каждого чипа DRAM составляет 16 Гб. На конец 2022 по той же технологии была представлена модель 1Тб плашки памяти (правда на момент выхода данной статьи, такая память не запущена еще в серию). Про стоимость такой памяти конечно можно скромно умолчать и только мечтать о выходи в массовый сегмент…

Все эти банки имеют общие шины команд, адресов и данных, что упрощает структуру системы памяти. Пока один банк занят работой с одной командой, другие банки могут продолжать выполнение своих операций. За счет чего увеличивается общая производительность обработки данных в памяти.

В свою очередь весь этот «сэндвич» чипа, содержащий все банки памяти и периферию, упакован в защитную оболочку и припаян к общей плате. Она содержит электропроводники, подающие питание и различные сигналы для работы DRAM. На крышку самого чипа обычно наносится маркировка производителя. Например, ниже представлен чип компании Micron.

Компаний-изготовителей чипов памяти не так уж и много на самом деле. По современной оценке, где-то вплоть до 90% всех мировых производственных объемов принадлежат «большой тройке» в лице Samsung, Micron и SK Hynix. Остальное делят между собой гораздо более мелкие игроки рынка, типа Nanya, Renesas, ESMT и прочих.

За тем к процессу подключаются различные вендоры, производящие уже сами платы DIMM — они берут несколько чипов DRAM с одинаковыми характеристиками и устанавливают их на одну такую плату. И соответственно эти же вендоры определяют разные конечные характеристики для своих плат памяти, в том числе наличие\отсутствие XMP-профиля, радиатора для отвода тепла и т.д.

Таких компаний гораздо больше на рынке и их количество насчитывается уже сотнями. Вот список лишь их небольшой части: Corsair, Gskill, Kingston, Goodram, Adata, Patriot, Crucial, Netac и множество других. К слову, сами же производители чипов, например те же Samsung, производят в том числе и платы DIMM под собственным брендом (та самая пресловутая «зеленая» самсунговская память), хотя они и не так сильно распространены на рынке домашних ПК.

Про специфику DIMM и ранги памяти

Мы уже отмечали ранее, что в природе существуют разные типы плат памяти, будь-то DIMM, SIMM, RIMM и т.д. Исторически при этом дошли далеко не все до наших дней. Сегодня в фактически любом магазине компьютерной техники вы встретите с вероятностью 99,9%, разве что только платы DIMM, либо ее «лептопную» разновидность SO-DIMM (используется в ноутбуках и неттопах) современных стандартов.

Форм-факторы плат памяти, которые сегодня обычно уже не встретишь

Хотя буква «D», в плате типа DIMM, расшифровывается как Dual (двойная) - это не значит, что на ней скажем два набора чипов или удвоенная пропускная способность. Под «двойным» тут идет речь о количестве электрических контактов в нижней части платы; для работы с модулями используются обе стороны платы (а однорядно-контактные платы обозначались ранее соответственно как SIMM).

Платы DIMM могут иметь разный форм-фактор (размер платы, например SO-DIMM), разные версии стандартов DDR (вплоть до DDR5) и разное количество чипов памяти на плате. Что касается именно чипов памяти, то существует как минимум три основных причины для использования нескольких их штук на одной плате DIMM:

- В один момент времени возможен доступ только к одному банку памяти внутри чипа и благодаря работе остальных банков в других чипах, повышается общая производительность памяти.

- В современных процессорах шина адреса (составляющая 64 бита) шире, чем шина одной единственной DRAM (обычно 8 бит). Поэтому к контроллеру памяти* можно подключить сразу несколько DRAM (например, по схеме: 8 модулей по 8 бит).

- Увеличивается общий объём доступного хранилища. Т.е. при среднем объеме современных чипов в 1–4 Гб, общий объем памяти на одной плате DIMM будет 8–32 Гб соответственно.

*Контроллер памяти — это специальная цифровая схема, управляющая потоком данных к(от) оперативной памяти. Сегодня является неотъемлемым функциональным блоком процессора, т.е. в современных системах находится внутри (под крышкой) самого CPU. Хотя ранее можно было встретить и в виде отдельной микросхемы, обычно именующейся «северный мост», на материнской плате.

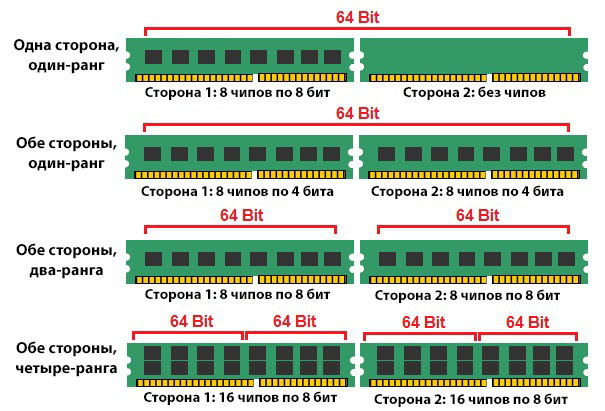

Совокупность множества чипов DRAM, взаимодействующих с шиной данных контроллера памяти, называется рангом (англ. Rank). Ранг памяти — это суммарное количество чипов памяти, совокупная разрядность которых составляет 64 бита. Чипы объединенные в ранг — подключены к одной линии выбора (chip select) на плате.

В принципе к контроллеру можно подключить больше одного ранга. За один проход контроллер сможет получать данные только от одного такого ранга, ибо ранги все-таки используют одну общую шину данных в 64 бита. Если упрощенно, то двух-ранговый модуль памяти для контроллера процессора воспринимается, как два логических модуля, распаянных на плате DIMM и использующих поочерёдно один физический канал передачи данных.

Взаимодействие одна-ранговой и двух-ранговой памяти с контроллером

Из сказанного выше мы понимаем, что платы DIMM могут иметь несколько рангов. Это особенно полезно, когда вам нужно огромное количество памяти и при этом на материнской плате мало слотов под платы DIMM. Разумеется материнская плата, как и сам процессор, должны уметь поддерживать «ранговость» памяти.

Так называемые схемы с двумя (Dual-rank) или даже четырьмя (Quad-rank) рангами потенциально могут предоставить большую производительность и емкость памяти, чем одноранговые, но и имеют обратную сторону медали — увеличение количества рангов быстро повышает нагрузку на электрическую цепь и соответственно требуют гораздо большего питания и более существенный теплоотвод.

Кстати, вопреки расхожему мнению, количество чипов памяти распаянных с одной, либо с обеих сторон платы DIMM далеко не всегда говорят напрямую о «ранговости» памяти и по сути определяется только спецификацией конкретной платы DIMM. Т.е. не всегда только лишь визуально можно распознать количество рангов памяти. В идеале информация об этом должна быть указана производителем в спецификации памяти или зашита в микросхему SPD (Serial Presence Detect — специальный модуль ПЗУ на плате DIMM содержащий информацию о таймингах, частотах и прочей спецификации памяти).

Платы DIMM с разным количеством рангов и чипов

Большинство материнских плат и CPU «домашнего» сегмента способны справиться только с одним или двумя рангами. Если системе нужно больше двух рангов, то используется DIMM с буферизацией (англ. Registered Memory, или иногда еще Buffered Memory) или сокращенно RDIMM. Такие платы имеют дополнительный чип (т.е. специальный буфер), облегчающий нагрузку на систему благодаря отдельному хранению команд и данных в течение нескольких циклов, прежде чем передать их дальше.

Обычно это специальная серверная память или память для рабочих станций, и для них нужны также специальные материнские платы и CPU. Некоторые из них способны работать с современными серверными платами DIMM вплоть до 8 (!) рангов (обычно по 32 чипа на плате).

Множество модулей памяти Nanya и один буферный чип — классическая серверная RAM

Стоит помнить, что шина данных имеет стандартную ширину в 64 бита. Но используемые в серверах и специальных рабочих станциях DIMM идет часто размером 72 бита, то есть на них установлен еще один дополнительный чип DRAM (т.е. используется 9 чипов на ранг, вместо стандартных 8). Этот дополнительный чип не обеспечивает повышение объёма или производительности. Он используется для проверки и устранения ошибок (англ. error checking and correcting); или как сокращенно называют такую память — ECC RAM.

Шина данных в такой памяти всё равно имеют ширину всего 64 бита, но надёжность хранения данных значительно повышается. В целом же использование памяти типа ECC REG RAM (в классической серверной памяти обычно применяется одновременно и модуль буфера, и модуль ECC) немного повышает общую производительность и надежность данных, но и в тоже время сильно повышает стоимость памяти, а также накладывает некоторые другие ограничения, например скромные возможности того же «оверклокинга» (хотя в серверах это понятие не встречается как класс).

Это интересно! Не так давно SK hynix сообщала о создании сверхбыстрой серверной памяти DDR5 с применением технологии Multiplexer Combined Ranks (MCR). С помощью специального чипа (разработанного Renesas совместно с Intel) и выступающего в роли буфера данных между центральным процессором и модулем ОЗУ, появилась возможность одновременно задействовать сразу два ранга памяти для увеличения ширины канала данных до 128 бит вместо привычных 64 бит. Правда самих процессоров, поддерживающих данную технологию, на момент написания статьи, на рынке еще не представлено.

Стандарт DDR и его эволюция

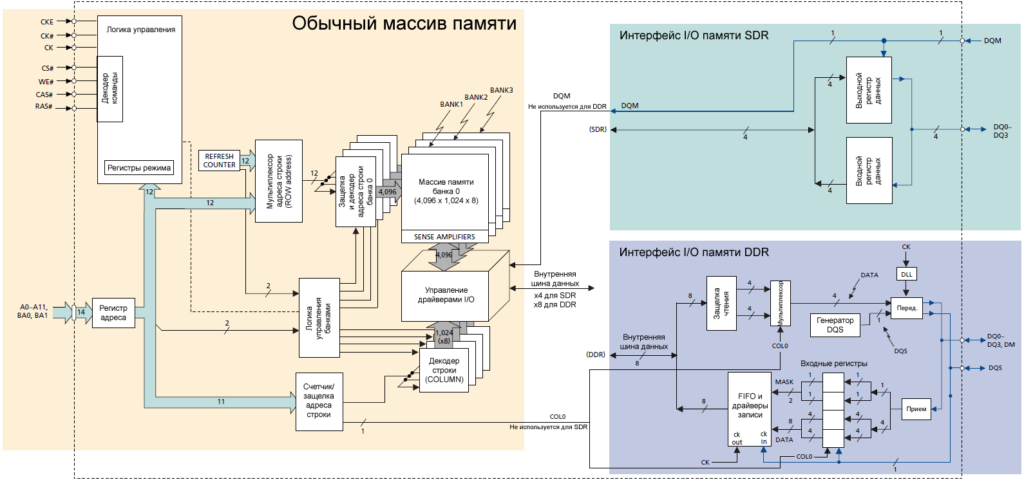

Не вдаваясь в глубокие архитектурные особенности памяти, отметим одно: у всех чипов DRAM есть так называемый интерфейс сигналов ввода-вывода, он же интерфейс I/O (input/output) — отвечающий за напряжение, постоянно переключающееся между двумя уровнями (в виде своеобразной синусоиды на графике ниже). Этот интерфейс используется для упорядочивания всех сигналов, что выполняются в чипе.

Ниже представлена блок-схема (которую стоит изучить лишь бегло, дабы не травмировать мозг) чипа памяти и интересов I\O двух разных типов — SDR и DDR.

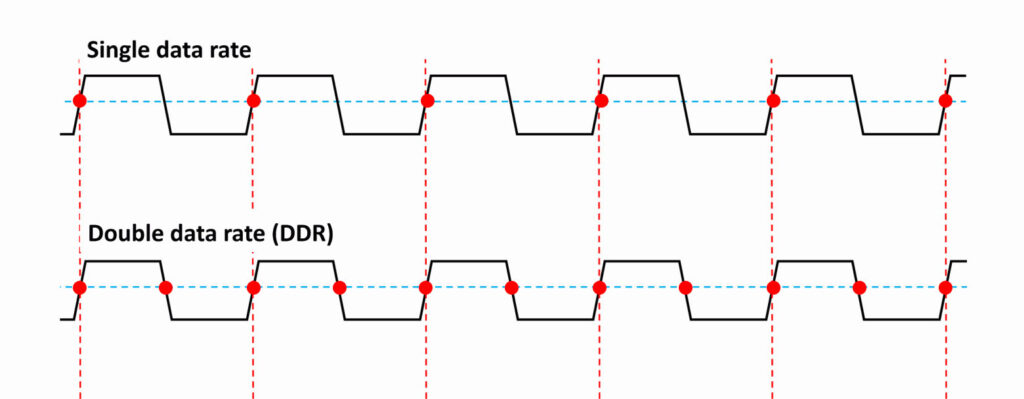

Если бы мы вернулись назад в 90-ые годы прошлого столетия, то смогли бы приобрести память типа SDRAM (синхронная DRAM), которая упорядочивала все процессы с помощью периода переключения тактового сигнала из низкого в высокое состояние. В те времена SDRAM имела тактовые сигналы ввода-вывода, обычно работавшие с частотой от 66 до 133 МГц, и за каждый такт сигнала в DRAM можно было передать только одну команду.

Быстрое развитие SDRAM, ведущей силой которого была корпорация Samsung, привело к созданию в 1998 году её нового типа. В нём передача данных синхронизировалась по повышению и падению напряжения тактового сигнала, где данные за каждый такт можно было дважды передать в DRAM и обратно.

Сравнение тактов SDR и DDR

Как же называлась эта восхитительная новая технология? Double data rate synchronous dynamic random access memory (синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных). Обычно её называют DDR-SDRAM или для краткости просто DDR. Память этого типа быстро стала стандартом и в течение последующих десятилетий оставалась и остается до сих пор лишь (меняя версии стандартов) неотъемлемой частью всех компьютерных систем.

Кстати, покупая модуль DIMM, например со спецификацией DDR4 3200 Mhz, по факту реальная частота памяти составляет всего 1600 Mhz и именно она, как правило, будет отображаться в утилитах (типа CPU‑Z) собирающих информацию о модулях памяти. А вот эффективная частота памяти умножается уже на два (т.к. сигнал передается дважды за такт) и получается то самое значение заявленное производителем, указанное на этикетке.

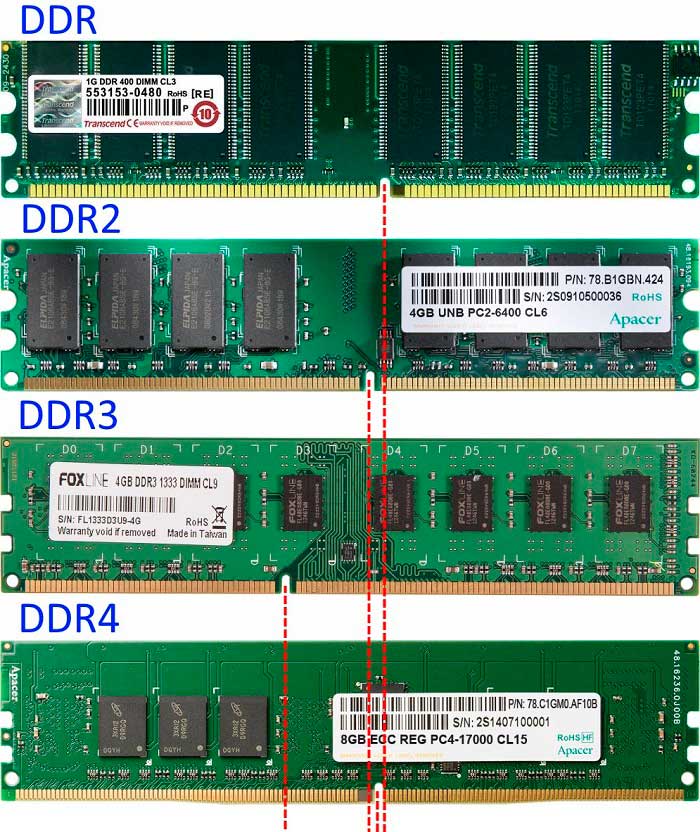

Разумеется прогресс технологий не стоял на месте. Удалось усовершенствовать эту память, благодаря чему в 2003 году появилась память типа DDR2, а уже в 2007 году и DDR3. Не заставила себя ждать и DDR4 появившаяся на свет в 2012 году, а вслед за ней и самая свежая на сегодня спецификация DDR5 явившейся миру в 2020 году. Глобально, каждая новая версия обеспечивала повышение производительности благодаря ускорению тактового сигнала ввода-вывода, увеличению размеров предварительной выборки и снижению энергопотребления.

DDR2 — внесла изменение, которое используется и сегодня: генератор тактовых сигналов ввода-вывода превратился в полноценную отдельную систему, время работы которой задавалось отдельным набором синхронизирующих сигналов, благодаря чему она стала в два раза быстрее. Это аналогично тому, как CPU используют для упорядочивания работы тактовый сигнал шины (BCLK) 100 МГц, хотя внутренние синхронизирующие сигналы могут работать в 30–40 или даже более раз быстрее.

DDR3 и DDR4 — сделали еще шаг вперёд, увеличив скорость тактовых сигналов ввода-вывода в четыре раза, хотя шина данных для передачи/получения информации по-прежнему использует только повышение и падение уровня сигнала ввода-вывода (т.е. удвоенную частоту передачи данных).

DDR5 - также внесла существенные архитектурные улучшения. Удвоилось количество банков памяти на чип и длина серийной очереди, добавилась новая команда SAME-BANK Refresh, которая позволяет обновлять только один банк памяти в каждой группе банков, а не все банки. На платах DIMM появилась встроенная схема управления питанием, появилась коррекция ошибок ECC даже в «потребительской» памяти. Произошла разделение шины на две 32 битные линии, вместо одной 64 битной, как ранее. Все это позволило в среднем увеличить пропускную способность памяти в 1,36 раза по сравнению с DDR4 при аналогичных частотах.

Но на самом деле сами по себе чипы памяти не работают на огромных скоростях, они «шевелятся» довольно медленно. Частота передачи данных (измеряемая в миллионах передач в секунду — millions of transfers per second, MT/s) в современных DRAM настолько высока благодаря использованию в каждом чипе нескольких банков; если бы на каждый модуль приходился только один банк, всё работало бы чрезвычайно медленно.

| Тип DRAM | Обычная частота чипа | Эффективная частота передачи данных | Пропускная способность | Напряжение, В | Год выпуска первых серийных модулей |

| SDR | 100 МГц | 100 MT/s | 1.6 ГБ/с | 3.3 | 1993 |

| DDR | 100 МГц | 200 MT/s | 3.2 ГБ/с | 2.5 | 2000 |

| DDR2 | 200 МГц | 800 MT/s | 8.5 ГБ/с | 1.8 | 2003 |

| DDR3 | 200 МГц | 1600 MT/s | 8.5 ГБ/с | 1.8 | 2007 |

| DDR4 | 400 МГц | 3200 MT/s | 25.6 ГБ/с | 1.2 | 2014 |

| DDR5 | 800 МГц | 6400 MT/s | 32 ГБ/с | 1.1 | 2021 |

Как мы можем видеть из таблице выше не смотря на то, что эффективная частота передачи данных от стандарта DDR до DDR5 увеличилась более чем в 60 (!) раз, а производители плат памяти рапортуют о каких-то феноменальных частотах в их «оверклокерских» решениях (на момент написания статьи представлена самая «топовая» DDR5 память частотой 8000 MT/s) общая итоговая пропускная способность такой памяти все-таки не может похвастаться столь выдающимся приростом показателей. Этому есть свое объяснения, но к нему мы вернемся позже.

Стоит также отметить, что особенностью каждой новой версии памяти является отсутствие обратной совместимости. То есть платы DIMM, используемые для чипов каждого нового стандарта, имеют разные количества электрических контактов и смещение вырезов (ключей), чтобы пользователь не мог вставить условную DDR3 в разъём для DDR2, или скажем DDR2 в слот DDR4 и т.д.

Смещение ключей плат DIMM в зависимости от стандарта

Кстати, есть ещё спецификация LP-DDR(X) для варианта памяти с низким энергопотреблением для таких устройств, как смартфоны. LP-DDR обычно позволяет выбрать варианты из двух-трех частот (например 1866 или 2133 Mhz для LP-DDR4X), чтобы можно было жертвовать скоростью ради энергопотребления. А есть ещё стандарты GDDR – уже вплоть до GDDR6X – для обработки графики и других высокоскоростных приложений.

Из интересных наблюдений можно отменить, что несмотря на новые стандарты, архитектурные решения и уменьшение напряжений с каждым новым поколением, тепловыделение чипов все равно остается на умеренно-высоком (а местами и очень высоком) уровне, т.к. в тоже время растут и частоты такой памяти, и плотность компоновки элементов чипа. Именно поэтому чипы памяти (особенно для GPU) обычно охлаждаются дополнительными внешними теплоотводящими элементами, типа медных или алюминиевых радиаторов.

Многоканальный режим работы памяти

В предыдущих разделах статьи мы выяснили, что оперативная память довольно крутая и быстрая штука. Она гораздо быстрее любах современных интерфейсов и накопителей в ПК, кроме разве что кэшей и регистров, находящихся внутри процессора. Вот только современные центральные процессоры, благодаря большому количеству встроенных в них ядер, настолько «ненасытны», что требуют еще больше скорости. И хотя тема внутреннего устройства современных CPU — это тема отдельная, мы все таки зацепим маленький ее кусочек, связанный с котроллером памяти.

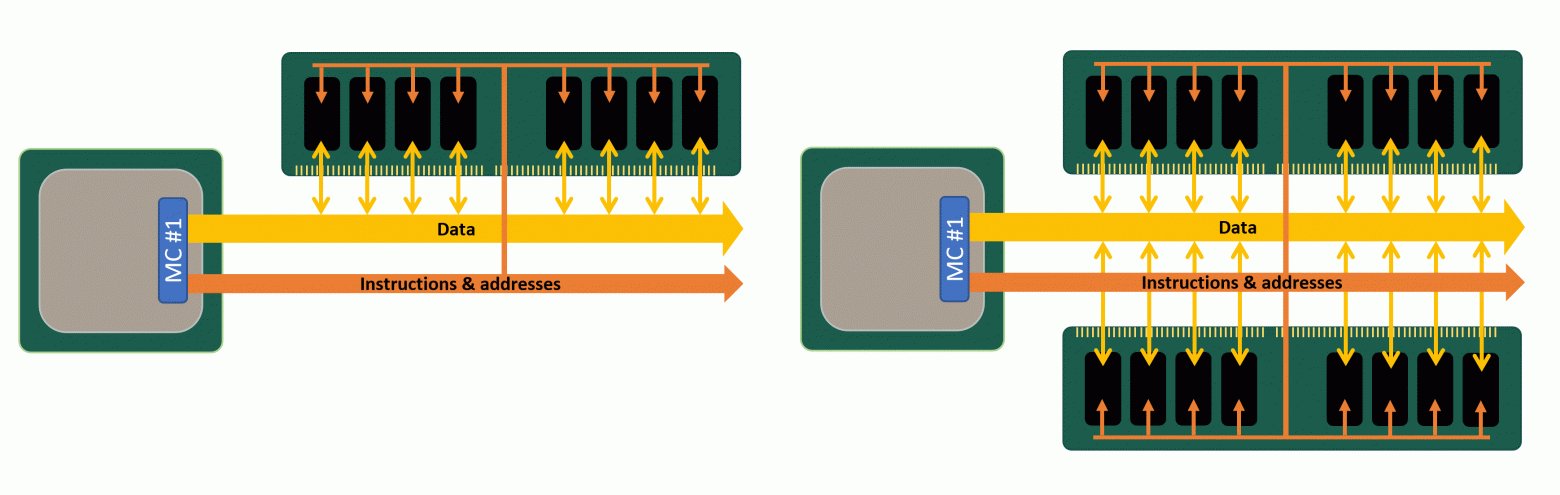

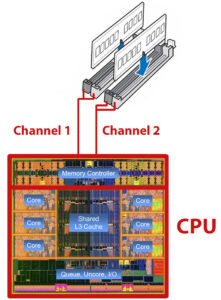

С развитием микропроцессорной архитектуры производители пришли к простой истине: «а почему бы не реализовать сразу несколько контроллеров памяти связанных между собой общей шиной?». То есть два или больше, очень грубо, независимых контроллера, каждый из которых работает со своими планками памяти. А если же к одному из контроллеров память не подключена, то этот контроллер ничего и не делает собственно — все просто, как дважды два!

Естественно контроллеры на самом деле не независимые полностью, так как все-таки имеет место быть общая адресация памяти и шина соединяющая кэш процессора и блок котроллера (состоящий из нескольких отдельных 64-битных контроллеров, соединенных с каждым каналом памяти). Но в части работы с памятью — можно считать их раздельными. Ну и работают эти контроллеры параллельно, а значит и пропускная способность их работы удваивается, учетверяется и т.д.

По крайней мере так предполагается в теории — на практике же, т.е. в реальных задачах, к сожалению ни о каком «удвоении-учетверении» речи обычно не идет и все сводится лишь к 10–30% прибавке скорости; но этот грустный момент мы скромно опустим и оставим для темы устройства современных CPU в отдельной статье.

Упрощенный принцип работы следующий. После того, как в модуле памяти сигнал пробежался по всем необходимым ему ячейкам памяти, строкам, столбцам, банкам и т.д. — при помощи усилителей сигнала он «пинком» вылетает, предварительно синхронизировавшись через интерфейс I\O, из микросхемы DRAM и летит к процессору (а точнее сначала к контроллеру памяти) по своему каналу памяти.

Многоканальный режим работы подсистемы памяти (англ. interleaving) и состоит собственно в том, что блоки данных распределяется между модулями памяти, подключенных в разных каналах контроллера памяти.

В обычном случае (одноканальный режим), во время обращения к памяти, никакие другие обращения к памяти производиться не могут. При работе в многоканальном режиме, соседние по виртуальным адресам ячейки размещаются в различных модулях памяти, и появляется возможность производить несколько операций одновременно. За счёт такого распараллеливания достигается выигрыш в скорости записи и чтения данных.

Сейчас мы не будем влазить в дебри инклюзивно-эксклюзивности кэша процессора, влияния канальных конфликтов и влияния количества ядер процессора на пропускную способность памяти, факторов «процессорного голода», вследствие простоя конвейера и т.д. Отметим лишь (да вы и сами уже наверняка поняли), что многоканальный режим работы памяти — это хорошо и правильно, а одноканальный — это «фу, бяка».

Разумеется, как и в случае с «ранговостью» памяти, многоканальность должна поддерживаться как самими CPU, так и материнской платой. Домашние системы обычно поддерживают одно- и двух-канальный режим работы памяти. В так называемом HEDT-сегменте (специальные рабочие станции) количество каналов может доходить до 4. В современном высокопроизводительном серверном сегменте поддерживается до 6 или даже до 8 каналов памяти!

Также стоит отметить чисто технический факт — чтобы многоканальный режим памяти в принципе работал (помимо непосредственной поддержки такого режима самим контроллером памяти), необходимо соблюдать принцип кратности установленных планок памяти. А также использовать для этих целей определенные по номерам слоты (каналы) памяти на материнской плате.

Пример подключения планок ОЗУ в 4‑х канальном режиме

Например, при 4‑х канальном режиме потребуется либо 4, либо 8 планок ОЗУ (в последнем случае контроллер будет работать разумеется также в 4 канальном режиме, просто скорость каждого канала будет, как бы «делится» между 2 плашками ОЗУ). При установке же всего 2 планок — контроллер перейдет в 2‑х канальный режим.

Справедливо и обратное, т.е. если контроллер процессора позволяет работать максимум в 2‑х канальном режиме, то установка 4 планок ОЗУ разумеется не заставит перевести его работу в 4‑х канальный режим, а будет работать в «поочередном» 2‑х канальном.

Про тайминги и задержки памяти

Мы уже выяснили, что производительность DRAM обычно измеряется в количестве битов данных, передаваемых за секунду. Также ранее в этой статье мы говорили, что используемая в качестве системной памяти DDR имеет чипы, как правило, с 8‑битной шириной шины, то есть каждый модуль может передавать до 8 бит за тактовый цикл.

Так если частота передачи данных чипа за такт равна 3200 MT\s, то его пиковый результат равен 3200 x 8 = 25 600 Мбит\с или чуть больше 3 Гб\с. А так как большинство DIMM имеет 8 чипов (на ранг), потенциально можно получить ~25 Гб\с.

Обычно это значение называют полосой пропускания (bandwidth) памяти; оно является важным фактором, влияющим на производительность RAM. Помножив это еще и на фактор многоканальности памяти — можно получить просто чудовищную скорость обработки данных, если бы не одно НО:

ВСЕ ЭТО ТЕОРИТИЧЕСКИЕ ВЕЛИЧИНЫ, НА ПРАКТИКЕ ОБЫЧНО НЕ ДОСТЕЖИМЫЕ!

Во-первых, все операции внутри чипа DRAM не происходят одновременно. На первом этапе активируется страница DRAM, в которой содержатся требуемые данные. Для этого памяти сначала сообщается, какой требуется ранг, затем соответствующий модуль (чип), а затем конкретный банк памяти (на самом деле в современных модулях банки объединяются в группы, как правило по 4 штуки, т.е. сначала определяется конкретная группа, а уже потом выбирается конкретный банк памяти).

Чипу передаётся местоположение страницы данных (адрес строки). На всё это требуется время и, что более важно, время нужно и для полной активации всей строки, чтобы гарантировать полную блокировку строки битов перед выполнением доступа к ней. Затем определяется соответствующий столбец и извлекается единственный бит информации.

Любая DRAM передает данные пакетами фиксированной длины (англ. Burst Length), где длина одного пакета, в современной памяти типа DDR4, равна 8 битам. То есть даже если за один тактовый цикл извлекается один бит, эти данные нельзя передать, пока из других банков не будет получено ещё 7 битов. А если следующий требуемый бит данных находится уже на другой странице, то перед активацией следующей необходимо закрыть текущую открытую страницу — этот процесс называется pre-charging. Всё это, разумеется, требует также время.

Во-вторых, имеет место быть и сама физическая структура, и технические ограничение DRAM. Физическое расположение ячеек внутри чипа памяти, логика работы ее периферии (блок I\O), качество исполнения линий связи ячеек памяти и общее качество самого «кремния» — все это также вносит свою лепту в задержки сигнала. Даже качество платы DIMM и длина дорожек от процессора к слотам памяти могут также на это влиять.

В конечном счете все эти различные периоды между временем отправки и фактическим выполнением команды называются таймингами памяти, измеряемые в тактах (циклах). Чем ниже это значение, тем ниже задержка сигнала (англ. Ram Latency, измеряется в «ns», т.е наносекундах) и выше общая производительность, ведь мы тратим меньше времени на ожидание завершения операций.

Принцип очень простой. Допустим тайминг CL (CAS Latency) равен 16, а тактовая частота DRAM 3200 Mhz (на самом деле, как мы помним не Mhz, а MT/s, но современные маркетологи вынуждают нас прибегать к общепринятой вакханалии названий и обозначений характеристик). Формула расчета задержки будет такой: 16×2000÷3200 = 10нс, где 2000 — это константа. Формула справедлива для расчета почти всех таймингов памяти.

У каждого такого тайминга есть свое название и их на самом деле достаточно много. Некоторые из этих таймингов очень хорошо знакомы фанатам «оверклокинга» (англ. Overclocking - или в простонародье «разгон железа»). Вот несколько примеров:

| Название тайминга | Описание | Обычное значение в DDR4 2133 Mhz |

| CL | CAS Latency: время между отправкой в память адреса столбца и началом передачи данных. Т.е. время, требуемое на чтение первого бита из памяти, при открытой строке. | 15 тактов |

| tRCD | Row-to-Column Delay: число тактов между открытием строки и доступом к столбцам в ней. т.е. время, требуемое на чтение первого бита из памяти без активной строки. | 17 тактов |

| tRP | Row Precharge time: число тактов между командой на предварительный заряд банка (закрытие строки) и открытием следующей строки. Т.е. время, требуемое на чтение первого бита из памяти, когда активна другая строка. | 17 тактов |

| tRAS | Row Cycle Time: число тактов между открытием строки и доступом к столбцам в ней. Т.е. время, требуемое на чтение первого бита из памяти без активной строки — должно быть не менее, чем RCD + CL. | 35 тактов |

Вышеперечисленные 4 тайминга в простонародье называются «первичными». И обычно они записываются производителем памяти в спецификации конкретной платы DIMM и на ее упаковке, в виде последовательности цифр каждого из этих таймингов. Причем именно в таком порядке: CL-RCD-RP-RAS, например 13−15−15−28, как на указанной ниже плате от производителя Corsair.

Пусть читателя не смущает слово «первичные», т.к. также выделяют условно «вторичные», «третичные» и даже «четверичные» тайминги. Вся это условная группировка пришла из мира оверклокинга, ибо самих таймингов насчитывается по меньшей мере около полусотни. И эти тайминги энтузиасты должны были как-то группировать между собой для понимая, какие из них при изменении влияют больше, а какие меньше на производительность памяти в целом.

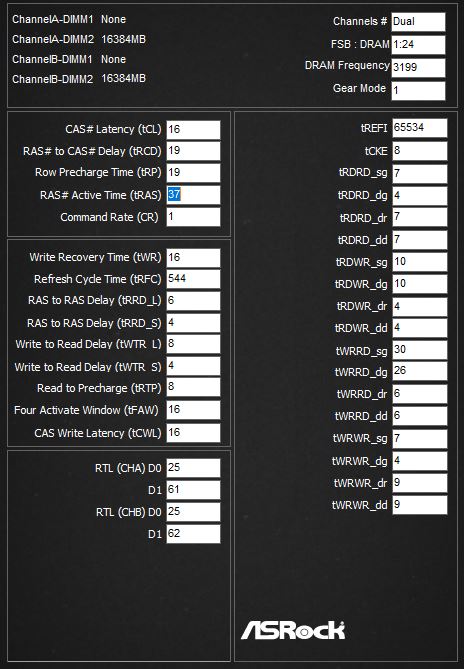

Пример списка всех доступных для изменения таймингов через ПО ASRock Timing Configurator

Чтобы DRAM работала стабильно и не искажала данные, имея при этом оптимальную производительность, все тайминги должны быть тщательно подобраны и настроены. Разумеется все это остается на откуп самих производителей плат памяти, хотя и в большинстве случаев потребителям оставляют «лазейку» в виде ручной настройки таймингов, если это конечно позволяет сама материнская плата.

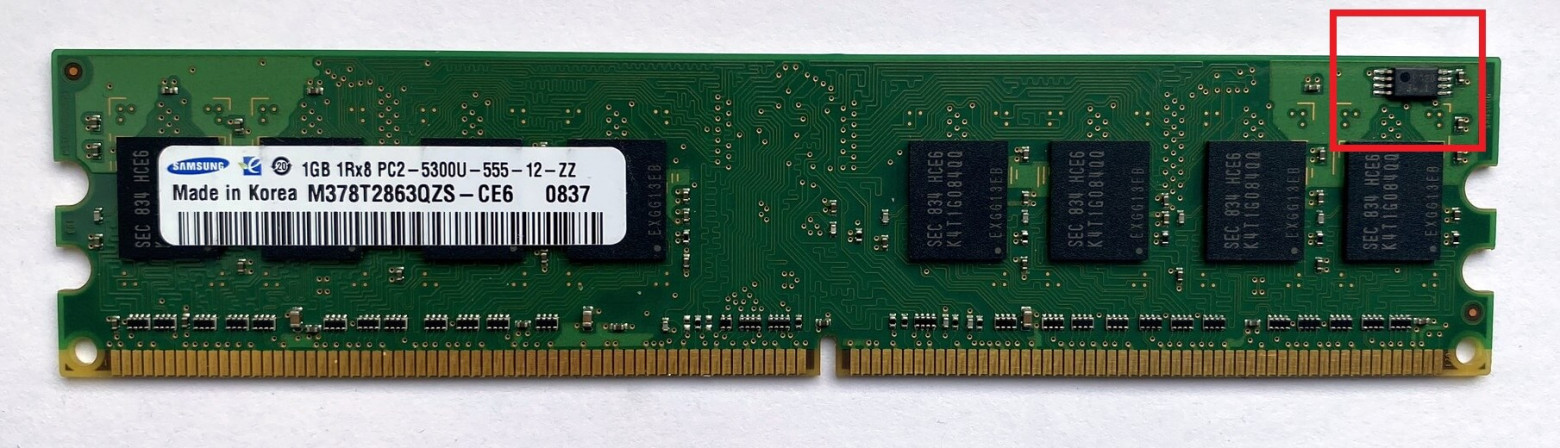

По итогу тайминги памяти можно настраивать — они не заданы жёстко в самой DRAM, потому что все команды поступают из контроллера памяти в процессоре, который использует эту память. Производители тестируют каждый изготавливаемый чип и те из них, которые соответствуют определённым скоростям при заданном наборе таймингов, группируются вместе и устанавливаются в плату DIMM. Затем тайминги сохраняются в небольшой чип, располагаемый на плате.

Процесс доступа к этой информации и её использования называется serial presence detect (сокр. SPD). Это отраслевой стандарт, позволяющий BIOS материнской платы узнать, на какие тайминги должны быть настроены все процессы. Обычно информация об SPD «зашивается» на специальную память ROM и распаивается на плате DIMM. Как видим даже для работы памяти нужна память 🙂

Блок ПЗУ (ROM), в котором содержится информация SPD.

Как уже отмечалось выше, это не жестко заданные параметры, а своего рода некоторые рекомендации, сообщающие контроллеру памяти, что вот эта конкретная планка DIMM протестирована и гарантирована может работать на указанных таймингах. Многие материнские платы позволяют пользователям изменять эти тайминги самостоятельно — для улучшения производительности или для повышения стабильности платформы, но чаще исключительно из маркетинговых соображений. Ведь чем лучше память поддается этим настройкам (чем ниже тайминги при более высокой частоте памяти), тем дороже сами модули для конечного потребителя.

Казалось бы, на первый взгляд две одинаковые планки DIMM от одного производителя, вроде бы равные и по объему, и по частоте, и по наличию «допиков» (в лице, например, радиатора для охлаждения чипов), лежащие на одной полке магазина, но имеющие разные тайминги, например 18−20−20−42 и 14−14−14−34 соответственно, могут достигать двух-трех кратной разницы в стоимости между собой! При том, что итоговая производительность такой памяти будет отличаться от силы в 5–7%.

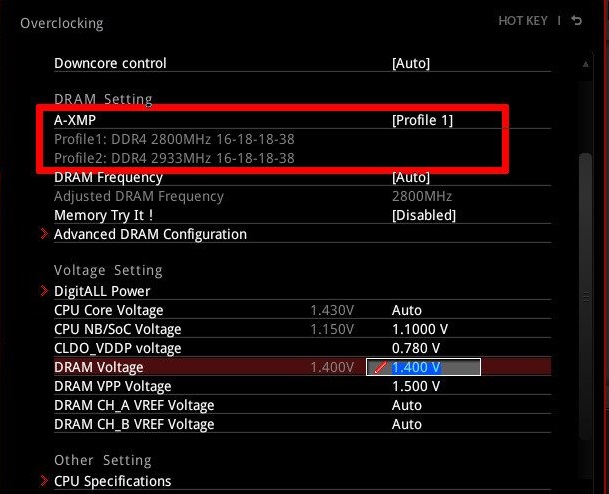

Многие модули DRAM также поддерживают специальный стандарт Extreme Memory Profile (сокр. XMP) компании Intel. Это просто дополнительная информация, хранящаяся также в памяти SPD, представляющая собой набор предустановленных программных профилей с уже настроенными производителем значениями заданных частот, таймингов и напряжений. Поэтому вместо самостоятельной возни с параметрами пользователь может настроить их одним нажатием мыши, выбрав из доступного списка соответствующий профиль в BIOS.

Обычно производителями предусмотрено наличие хотя бы одного-двух таких профилей XMP. Многие современные DIMM c DDR5 на борту позволяют использовать даже до 5 таких профилей, причем 3 из них могут быть заданы производителем с завода, а самому пользователю может быть доступно самостоятельное создание еще пары таких профилей. Хотя стоит заметить, что настройки XMP профилей далеко не всегда могут быть оптимальными и это не отменяет обычно ручной настройки для еще большего «выжимания соков» из памяти для улучшения ее общей производительности.

Продолжение следуют

Вот и подошла к своему логическому завершению статья про DRAM. Надеюсь материал был кому-то полезен и интересен. И теперь у вас есть некоторое структурированное понимание работы современной памяти.

В следующих статьях мы затронем, пожалуй, и собрата в лице SRAM в современных ее проявлениях. Также «заглянем» в недра современных CPU и поговорим о регистрах и многоуровневом кэше процессора.

Как-нибудь разберем в отдельной статье и память ROM, со всеми ее проявлениями, в том числе и в современных SSD и других накопителях данных. Так что, как говорится — не переключайтесь 🙂